# Proving Correctness of Parallel Implementations of Transition System Models

FRANK S. DE BOER, CWI, the Netherlands

EINAR BROCH JOHNSEN, University of Oslo, Norway

VIOLET KA I PUN, Western Norway University of Applied Sciences, Norway

SILVIA LIZETH TAPIA TARIFA, University of Oslo, Norway

This paper addresses the long-standing problem of program correctness for programs that describe systems of parallel executing processes. We propose a new method for proving correctness of parallel implementations of high-level models expressed as transition systems. The implementation language underlying the method is based on the concurrency model of actors and active objects. The method defines program correctness in terms of a simulation relation between the transition system which specifies the program semantics of the parallel program and the transition system that is described by the correctness specification. The simulation relation itself abstracts from the fine-grained interleaving of parallel processes by exploiting a global confluence property of the concurrency model of the implementation language considered in this paper. As a proof of concept, we apply our method to the correctness of a parallel simulator of multicore memory systems.

${\tt CCS\ Concepts: \bullet Theory\ of\ computation} \rightarrow {\tt Semantics\ and\ reasoning; Program\ specifications; Program\ verification.}$

Additional Key Words and Phrases: correctness, transition system models, active objects, simulation, multicore memory systems

#### **ACM Reference Format:**

#### 1 INTRODUCTION

A long-standing challenge in Computer Science is the formal specification and verification of programs, notably that of parallel programs supporting complex communication and synchronization mechanisms. We can distinguish between logic- and semantics-based methods for establishing program correctness. Methods that are based on logic use assertions to express behavioral properties and generate proof conditions for their validation, which are usually discharged by interactive theorem proving. These methods are applicable to infinite-state systems and to actual programs used in practice (see for example [24] for the verification of a corrected version of the TimSort sorting program of the Java Collections Framework). One of the main challenges for the use of logic-based approaches stems from the complexity of the specification of invariant properties and the interactive use of a theorem prover. On the other hand, semantics-based methods use transition

Authors' addresses: Frank S. de Boer, CWI, Amsterdam, the Netherlands, F.S.de.Boer@cwi.nl; Einar Broch Johnsen, University of Oslo, Oslo, Norway, einarj@ifi.uio.no; Violet Ka I Pun, Western Norway University of Applied Sciences, Bergen, Norway, Violet.Ka.I.Pun@hvl.no; Silvia Lizeth Tapia Tarifa, University of Oslo, Oslo, Norway, sltarifa@ifi.uio.no.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. Copyrights for components of this work owned by others than ACM must be honored. Abstracting with credit is permitted. To copy otherwise, or republish, to post on servers or to redistribute to lists, requires prior specific permission and/or a fee. Request permissions from permissions@acm.org.

© 2024 ACM.

ACM 0164-0925/2024/5-ART1

https://doi.org/10.1145/nnnnnn.nnnnnnn

systems to model system behavior. Transitions may be small-step or big-step, finite or infinite state, and support a range of verification methods including inductive reasoning and automated model checking (in the case of finite state models).

The main contribution of this paper is a new semantics-based verification method for parallel programs, exploiting the concurrency model of Actors [2] and active objects [23]. The method is based on specifying an abstraction of the overall behavior of a parallel program in terms of a transition system model (TS model, for short). The TS model describes behavior by means of the local transformation of states by application of symbolic transformation rules. Examples of formalisms that can be used to specify such TS models include the *Chemical Abstract Machine* [7], the rewriting system Maude [19],  $\mathbb{K}$  [51] and Structural Operational Semantics [50]. Verifying that a parallel program satisfies such a correctness specification then involves establishing a *simulation relation* between the transition system describing the semantics of the parallel program and the system described by the TS model (which may be infinite state). Although these systems are at different levels of abstraction and use different mechanisms for communication and synchronization, our proof method allows the simulation relation to be established by means of *syntax-directed local reasoning*. In this paper, the proposed proof method is justified in terms of the semantic properties of our targeted implementation language, which is an actor language with cooperative scheduling. Our method supports a general two-step approach to proving the correctness of parallel programs:

- (1) Verify global behavioral properties using a high-level formal model which abstracts from the complexity of the concurrency model of the target language to support inductive proofs of global properties.

- (2) Justify the correctness of the parallel implementation in the target language with respect to the high-level model in terms of a simulation relation.

For the first step, a TS model allows for the formal description of overall system behavior in a syntax-oriented, compositional way, using inference rules for local transitions and their composition. Process synchronization can be expressed abstractly using, e.g., conditions on system states and reachability conditions over transition relations as premises, and label synchronization for parallel transitions. This high level of abstraction greatly simplifies the verification of system properties. Whereas TS models are well-suited for formalizing language semantics and for reasoning about language meta-theory, they are also well-suited to describe specific systems in order to reason about, e.g., reachability or state invariance.

For the second step, we need an implementation in an Actor language with a formal semantics (e.g., formalized by a TS model), such that a simulation relation can be formally established. The concurrency model of Actors then enables proving correctness in terms of syntax-directed sequential reasoning. In this paper, we have opted for the *active object* language ABS [30, 52] (ABS stands for *Abstract Behavioral Specification*). The semantics of ABS is formally defined by a TS model [32] and implemented by backends<sup>1</sup> in Erlang, Haskell, and Java, all of which support parallel execution. It has been developed and applied in the context of various EU projects, e.g., in the EU FP7 projects HATS<sup>2</sup> (*Highly Adaptable and Trustworthy Software using Formal Models*) and ENVISAGE<sup>3</sup> (*Engineering Virtualized Services*). In these projects, ABS has been extended and successfully applied to the formal modeling and analysis of software product families [21] and software services deployed on the Cloud [34]. The ABS tool suite [3, 5, 8, 25, 26, 35, 37, 38, 53]

<sup>1</sup>https://abs-models.org/

<sup>&</sup>lt;sup>2</sup>https://cordis.europa.eu/project/id/231620

<sup>&</sup>lt;sup>3</sup>https://cordis.europa.eu/project/id/610582

has been further applied to case studies, targeting, e.g., cloud-based frameworks [4, 33, 42, 43, 59], railway operations [36] and computational biology.<sup>4</sup>

The parallel execution of active objects (for a survey of active object languages, see [23]) is a direct consequence of decoupling method execution from method invocation by means of *asynchronous* method invocations. ABS further integrates a strict *encapsulation* of the local state of an active object with explicit language constructs for the *cooperative scheduling* of its method executions. Since ABS is tailored to the description of distributed systems, it abstracts from the order in which method invocations are generated.

In the definition of the simulation relation, cooperative scheduling allows the interleaving of methods in an active object to match the granularity of the transition rules of the corresponding TS model. Moreover, the parallel execution of active objects in ABS satisfies a *global confluence* property which allows to express *locally* the proof conditions of the simulation relation in a syntax-directed manner, abstracting from the fine-grained interleaving of the method executions.

As a proof of concept we introduce our method by application to a parallel simulator of multicore memory systems. These memory systems generally use caches to avoid bottlenecks in data access from main memory, but caches introduce data duplication and require protocols to ensure coherence. Although data duplication is usually not visible to the programmers, the way a program interacts with these copies largely affects performance by moving data around to maintain coherence. To develop, test and optimize software for multicore architectures, we need correct, executable models of the underlying memory systems. A TS model of multicore memory systems with correctness proofs for cache coherency was described in [13, 14], together with a prototype implementation in the rewriting logic system Maude [19]. However, this fairly direct implementation of the TS model is not well suited to simulate large systems. Therefore this paper introduces a parallel implementation, based on the active object model of ABS; we apply our method to prove its correctness.

This paper extends [9] which describes a first version of the use case. The extension consists of formalizing the novel idea of annotating ABS programs with the rule names of the TS model and the use of a global confluence property of the ABS semantics in the formal semantics (and verification) of these annotations. Because of the absence of this high-level specification of the simulation relation between the ABS program and the TS model, the ABS implementation in [9] has been developed largely independent of the TS model, which considerably complicated the correctness proof. In contrast, the application of our new methodology led to a major refactoring of the ABS implementation described in [9], reflecting a correctness-by-design development methodology.

In summary, the main contributions of this paper are

- a novel semantics-based method for proving the correctness of parallel systems, based on the Actor model of concurrency,

- a justification of the method in terms of the semantic properties of the Actor concurrency model, and

- a proof-of-concept case study illustrating the application of the method to a parallel simulator of a multicore memory system.

Plan for the paper. The next section introduces the main concepts of the ABS language and Section 3 the use of transition rules as annotations of ABS programs. Section 4 explains the TS model of multicore memory systems and Section 5 considers its ABS implementation and the associated correctness proof. We discuss related work in Section 6, and draw some general conclusions and discuss future work in Section 7. Appendices A, B and C further detail the global confluence property, the correctness proof and the multicore TS model of the case study, respectively.

<sup>&</sup>lt;sup>4</sup>https://www.compugene.tu-darmstadt.de

| Statement                                           | Meaning                                          |

|-----------------------------------------------------|--------------------------------------------------|

| new C                                               | Creation of an instance of class C               |

| <b>switch</b> (e){ $e_1 => s_1 \cdots e_n => s_n$ } | Pattern matching                                 |

| <b>await</b> b                                      | Suspension on a Boolean condition                |

| <b>await</b> $e!m(e_1, \ldots, e_n)$                | Suspension on termination of a asynchronous call |

| $e!m(e_1,\ldots,e_n)$                               | Non-blocking asynchronous call                   |

| $e.m(e_1,\ldots,e_n)$                               | Blocking synchronous call                        |

| this.m $(e_1,\ldots,e_n)$                           | Inlined (recursive) self-call                    |

Table 1. Basic ABS statements used in this paper. Here, b is a Boolean expression, e and  $e_i$  denote expressions.

#### 2 ABS: ACTORS WITH COOPERATIVE CONCURRENCY

ABS is a modeling language for designing, verifying, and executing concurrent software [30, 52]. The core language combines the syntax and object-oriented style of Java with the Actor model of concurrency [31], resulting in active objects which decouple communication and synchronization using asynchronous method calls and cooperative scheduling [23]. In ABS communication (sending a method call) and execution (scheduling an incoming method call) are decoupled via asynchronous method calls that generate processes (which execute the called methods) within the called (active) object and do not impose any synchronization between caller and callee. Thus, the caller can continue execution until the result of a method call is needed, and the callee can schedule method calls from multiple callers as needed. When synchronization between two objects is needed (e.g., a process needs the result of a method call), it is realised by means of (implicit) futures and cooperative scheduling. In ABS, objects have state (fields and object parameters) which is shared between all its processes. However, only one process may execute at a time in any object (i.e., the objects have a built-in mutex). Similarly, processes also have their own state (local variable and parameters to the method calls). A process executing in one object can allow another process to be scheduled in the same object by means of explicit suspension points. The active process suspends itself when waiting for the result of another method call or waiting for a Boolean condition over the actor state, using an await-statement. Rescheduling the process at the suspension point may then depend on the resolution of a future or on a Boolean condition becoming true. This mechanism of cooperative scheduling allows the interleaving of different processes to be captured very precisely in ABS.

The imperative layer of synchronization and communication is complemented by a functional layer, used for computations over the internal data of objects. The functional layer combines parametric algebraic datatypes (ADTs) and a simple functional language with case distinction and pattern matching. ABS includes a library with predefined datatypes and operations (e.g., Int, Bool), including a datatype Maybe that is used to store optional values,<sup>5</sup> and parametric datatypes and associated functions (e.g., lists,<sup>6</sup> sets and maps). All other types and functions are user-defined.

In the following, the basic ABS-related statements used in this paper (and shown in Table 1) are explained in terms of some general synchronization patterns (we omit well-known statements such assignment, **skip**, **if**, **foreach**, **return**, etc.).<sup>7</sup>

<sup>&</sup>lt;sup>5</sup>The Maybe datatype is used when the functional code that is assigned to a variable may not return a value in all cases. If no value is returned, the default value is Nothing, otherwise the value is wrapped inside the Just construct, e.g., Just(True). Further details can be found in the ABS documentation https://abs-models.org/manual/#sec:builtin-types.

<sup>&</sup>lt;sup>6</sup>The parametric data type List<A> is defined as Nil | Cons(A head, List<A> tail), where A is a datatype.

<sup>&</sup>lt;sup>7</sup>For the full set of statements of ABS, we refer to the ABS documentation at https://abs-models.org/manual/#-statements. In ABS, method calls are not guaranteed to terminate since statements in the methods might include **while**-loops and recursive calls.

## 2.1 Synchronization Patterns

In this section, we discuss encodings in ABS of a basic locking mechanism, atomic operations, and a broadcast mechanism for global synchronization (using barriers).

Locks. The basic mechanism of asynchronous method calls and cooperative scheduling in ABS can be explained by the simple code example of a class Lock (Figure 1). It uses an **await**-statement on a Boolean condition to model a binary semaphore, which enforces exclusive access to a common resource "lock", modeled as an instance of the class Lock (instances are dynamically created by executing the expression **new** Lock).

The execution of the take\_lock method will be suspended by the **await** unlocked statement. This statement *releases the control*, allowing the scheduling of other (enabled) processes within the Lock object. When the local condition unlocked inside the Lock object has become true, the generated take\_lock processes within the Lock object will compete for execution. The scheduled process will then terminate and return by setting unlocked to False.

In general, the *suspension points* defined by **await**-statements define the granularity of interleaving of the processes of an object. The ABS statement **await** lock!take\_lock() will only suspend the process that issued the call (and release control in the caller object) until take\_lock has returned. In contrast, a *synchronous* call lock.take\_lock() will generate a process for the execution of the take\_lock() method by the lock object and block (all the processes of) the caller object until the method returns.

Atomic operations. The interleaving model of concurrency of ABS allows for a simple and high-level implementation of atomic

```

class Lock {

Bool unlocked = True;

Unit take_lock {

await unlocked;

unlocked = False; }

Unit release_lock {

unlocked = True; }

}

{// using the lock

... lock = new Lock();

await lock!take_lock;

... // critical resource

lock.release_lock();

}

```

Fig. 1. Lock implementation in ABS using await on Booleans.

operations. For example, Figure 2 shows a general ABS implementation of test-and-set instructions [6], where the concurrency model guarantees that the local /\*test(input)\*/ and /\*set\*/ statements, assuming that they do not involve suspension points, are not interleaved and thus can be thought of as executed in a single atomic operation. An instance of this atomic operation can be observed in the method remove inv in Figure 11.

In ABS test instructions can be implemented using the **switch**-statement, which evaluates an expression that matches the resulting value against a pattern  $\mathbf{e}_i^{\ 8}$  in the different branches. This statement has mainly been used to pattern match the ADTs used in the ABS program discussed in this paper. In the simplest case, this pattern can be replaced by an **if**-statement.

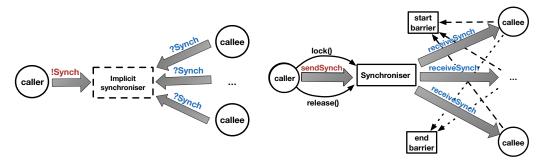

*Broadcast synchronization.* Figure 3a shows how broadcast synchronization in a labelled TS model can be enforced by simply matching labels (where exclamation marks and question mark denote sending and receiving a signal, respectively. An example

```

Bool TestandSet (/*input*/) {

Bool fail = False;

switch /*test(input)*/ {

True => /*set*/;

False => fail = True;

}

return fail;

}

```

Fig. 2. Test-and-set pattern in ABS.

is detailed in Section 4), thus abstracting from the implementation details of the implicit multiparty synchronizer. On the other hand, in programming languages for distributed systems like

$<sup>^8</sup>$ A pattern  $\mathbf{e}_i$  in the **switch**-statement can be an expression that includes a datatype constructor e.g., the list constructor Cons(h,t), in which case the local variables h and t are bound by the pattern matching and available in the statement  $\mathbf{s}_i$  associated to  $\mathbf{e}_i$ . Underscore \_ matches any pattern.

- a) Broadcast synchronization in a labelled TS model.

- b) Broadcast synchronisation using an explicit synchronizer and barriers in the ABS model.

Fig. 3. Broadcast synchronisation patterns in TS model and ABS.

ABS the multi-party synchronization needs to be programmed explicitly; Figure 3b illustrates the architecture of the ABS implementation shown in Figure 4.

The class Broadcast serves as a template (or design pattern) for the implementation of a broadcast mechanism between objects that are specified by the interface IBroadcast. The broadcastSync method encapsulates a synchronisation protocol between Broadcast instances which uses the additional classes Synchronizer and Barrier. This protocol consists of a synchronous call to the method sendSync of an instance of the class Synchronizer (denoted by sync) which in turn asynchronously calls the method receiveSync of the objects stored in the set network of Broadcast instances, excluding the caller object executing the broadcastSync method. We abstract from whether the sync object is passed as a parameter of the broadcastSync method or is part of the local state of any Broadcast instance. The local computation specified by the receiveSync method by the objects in receivers is synchronized by calls of the method synchronize of the new instances start and end of class Barrier. That is, the execution of this method by the start and end barriers synchronize the start and the termination of the execution of the method receiveSync by the objects in receivers and the termination of the sendSync method itself. This is achieved by a "countdown" of the number of objects in receivers that have called the synchronize method plus one, in case of the end barrier. The synchronize method of the start barrier is called asynchronously (Line 16) and introduces a release point in order to avoid a deadlock that may arise when an object that has not yet called the synchronize method of the start barrier is blocked on a synchronous method call to an object that has already invoked (synchronously) the synchronize method of the start barrier. On the other hand, the corresponding call to the end barrier is synchronous to ensure that all the objects in receivers have completed their local computations. The additional synchronisation of the synchronizer object on the end barrier ensures that also the caller of the sendSync method is blocked until all the local computations specified by the receiveSync method have been completed.

Objects in ABS are input enabled, so it is always possible to call a method on an object. In our implementation, this scheme could give rise to inconsistent states if several objects start the protocol in parallel. To ensure exclusive access to the synchronizer at the start of the protocol, we add a lock to the synchronizer protocol, such that the caller must take the lock before calling sendSync and release the lock upon completion of the call. The resulting exclusive access to the synchronizer guarantees that its message pool contains at most one call to the method sendSync.

```

interface | Broadcast {

1

Bool broadcastSync(...);

2

Unit receiveSync (IBarrier start, IBarrier end, ...)

3

4

5

class Broadcast implements IBroadcast, ... {

6

Bool broadcastSync(...) {

Bool signal=False;

8

await sync!lock();

if /*test*/{ sync.sendSync(this,...); /*set*/; signal=True; }

10

sync.release();

11

return signal

12

}

13

14

Unit receiveSync(IBarrier start, IBarrier end, ...) {

15

await start!synchronize();

16

/*some local computation*/;

17

end.synchronize();

18

}

19

20

21

22

class Synchronizer (Set<IBroadcast> network) implements ISynchronizer {

23

Bool unlocked = True:

24

25

Unit lock() { await unlocked; unlocked = False; }

Unit release() { unlocked = True; }

26

Unit sendSync(IBroadcast caller,...) {

27

Set<IBroadcast> receivers = remove(network,caller);

28

Int nrrecs= size(receivers);

29

IBarrier start = new Barrier(nrrecs);

30

IBarrier end = new Barrier(nrrecs+1);

31

foreach (receiver in receivers) { receiver!receiveSync(start,end,...); }

32

end.synchronize();

33

}

34

35

36

37

class Barrier(Int participants) implements IBarrier {

Unit synchronize() { participants = participants - 1; await (participants == 0); }

38

39

```

Fig. 4. Global synchronisation pattern in ABS.

#### 2.2 Semantics

ABS is a formally defined language [32]; in fact, its (operational) semantics is defined by a TS model which allows us to reason formally about the execution of ABS programs. The semantics of an ABS model can be described by a transition relation between global configurations. A global configuration is a (finite) set of object configurations. An object configuration is a tuple of the form  $\langle oid, \sigma, p, Q \rangle$ , where oid denotes the unique identity of the object,  $\sigma$  assigns values to the instance variables (fields) of the object, p denotes the currently executing process, and Q denotes a

set of (suspended) processes (the object's "queue"). A process is a closure  $(\tau, S)$  consisting of an assignment  $\tau$  of values to the local variables of the statement S. We refer to [32] for the details of the TS model for deriving transitions  $G \to G'$  between global configurations in ABS.

Although only one thread of control can execute in an active object at any time (taken by the active process), cooperative scheduling allows different processes to interleave by releasing the thread of control (allowing another suspended process to become active) at explicitly declared points in the code, i.e., the **await**-statements. When the currently executing process is suspended by an **await**-statement, another (enabled) process is scheduled. Access to an object's fields is protected: any non-local (outside of the object) read or write to fields happens via method calls, mitigating race-conditions or the need for extensive use of explicit mutual exclusion mechanisms (locks).

Since active objects only interact via method calls and processes are scheduled non-deterministically, which provides an abstraction from the order in which the processes are generated by method calls, the ABS semantics satisfies the following global confluence property (see also [9, 60]) that allows commuting consecutive local computations steps of processes which belong to *different* objects.

Theorem 1 (Global confluence). For any two transitions  $G_1 \to G_2$  and  $G_1 \to G_3$  that describe execution steps of processes of different objects, there exists a global configuration  $G_4$  such that  $G_2 \to G_4$  and  $G_3 \to G_4$ .

It is worthwhile to observe that this global confluence property follows from the following basic principles underlying actor-based languages:

- encapsulation of the local state,

- monotonicity of the local transitions which are not affected by adding messages and

- the basic algebraic laws of adding and deleting elements from a multiset (of messages).

In fact, global confluence can be proven in an abstract setting which captures the general semantics of actor languages, see Appendix A. Theorem 1 then follows by embedding the semantics of ABS into this abstract setting. The details of this embedding for the communication and synchronization mechanisms of ABS (method calls, **await**-statements and futures) are discussed in the appendix.

An important consequence of Theorem 1, which underlies the main results of this paper, is that we can restrict the global interleaving between processes by reordering the execution steps in an ABS computation. In particular, we can restrict the interleaving semantics of the ABS model taking into account general semantic properties of synchronous communication, and the implementation of locks and broadcast synchronization in ABS, as explained next.

Since a synchronous call to a method of *another* object in ABS, blocks all processes of the caller (object), the global confluence property allows further restricting the interleaving of the ABS processes so that the caller process is resumed *immediately* after the synchronous method invocation has terminated.

It is worthwhile to note that in general we *cannot* assume that a method that is called synchronously in ABS is also scheduled *immediately for execution* because this would discard the possible execution of other processes by the callee.

The global confluence property also allows for abstracting from the internal computation steps of the above ABS implementation of the global (broadcast) synchronization pattern, because it allows scheduling the processes generated by the *broadcast* method such that the execution of this method is not interleaved with any other processes.

We can formalize the above in terms of the following notion of *stable* object configurations. An object configuration is stable if the statement to be executed denotes the termination of an *asynchronously* called method (we let *idle* denote the terminated process), or it starts with a (blocking) synchronous call or an **await**-statement.

DEFINITION 1 (STABLE CONFIGURATIONS). Let S and S' be statements and  $\tau$  a local variable assignment. An object configuration  $\langle oid, \sigma, p, Q \rangle$  is stable if p denotes the terminated process idle or p denotes a process  $(\tau, S')$ , where S' denotes one of the statements

- $e.m(\overline{e}); S$ ,

- await b; S or

- await  $e!m(\overline{e}); S$ .

A global ABS configuration is stable if all its object configurations are stable.

Since synchronous self-calls are executed by inlining, they do not represent interleaving points. In the sequel  $G \Rightarrow G'$  denotes the transition relation which describes execution starting from a global stable configuration G to a next global stable configuration G' (without passing intermediate global stable configurations). We distinguish the following three cases:

- (1) The transition  $G \Rightarrow G'$  describes the *local* execution of a method by a single object.

- (2) The transition  $G \Rightarrow G'$  describes the *rendez-vous* between the caller and callee of a synchronous method call in terms of the terminating execution of the called method, *followed* by the resumption of the suspended call.

- (3) The transition  $G \Rightarrow G'$  describes the effect of executing the broadcast method, which thus describes the *global* synchronization of different objects.

This coarse-grained interleaving semantics of ABS forms the basis for the general methodology to prove correctness of ABS implementations of TS models, described next.

## 3 THE GENERAL METHODOLOGY

# 3.1 Annotating ABS Methods with Rules from the TS Model

For an introduction to TS models, see, e.g., [49]. The general methodology for developing ABS implementations of abstract TS models exploits the coarse-grained interleaving described in Section 2 (denoted by the transition relation  $\Rightarrow$ ). This course-grained interleaving allows us to focus on the design of *local*, *sequential* code that implements the individual transition rules. This is reflected by the use of transition rules as a *specification formalism* for ABS code. A *conditional transition rule* b:R consists of a local Boolean condition b in ABS and the name R of a transition rule. We use sequences  $b_1:R_1;\ldots;b_n:R_n$  of conditional transition rules to annotate *stable points* in ABS method definitions. A stable point in a method definition denotes either its body or a statement of its body that starts with an external synchronous call or an **await**-statement. The idea is that each  $b_i$  is evaluated as a condition which identifies a *path* leading from the annotated stable point to a next one or to termination. The execution of this path should correspond to the application of the associated transition rule  $R_i$ . This correspondence involves a simulation relation, described below.

A sequence  $b_1: R_1; \ldots; b_n: R_n$  of conditional transition rules is evaluated from left to right, that is, the first transition rule from the left, the Boolean condition of which evaluates to true, is applicable. The case that all Boolean conditions are false means that there does not exist a transition rule for *any* path from the annotated stable point to a next one or to termination (in the simulation relation, all these paths would correspond to a "silent" transition). As a special case, we stipulate that for *any* path leading from a stable point *which has no associated annotation* to a next stable point (or to termination), there does *not* exist a corresponding transition rule. The use of annotations in the ABS code of the multicore memory system is shown in Section 5.2.1.

# 3.2 Correctness of the Implementation

The correctness of the ABS implementation with respect to a given TS model can be established by means of a simulation relation between the transition system describing the semantics of the

ABS implementation and the transition system describing the TS model. The annotation of ABS code with (conditional) rules from the TS model provides a high-level description of the simulation relation, describing which rule(s) correspond to the execution of the ABS code from one stable point to a next one (or to termination). Underlying this high-level description, we define a simulation relation between ABS configurations and the runtime states of the TS model. This simulation relation is defined as an abstraction function  $\alpha$  which maps every stable global ABS configuration  $\alpha$  to a behaviorally equivalent configuration  $\alpha(G)$  of the TS model. The abstraction function for the ABS code of the multicore memory system is shown in Section 5.2.2.

We restrict the simulation relation to *reachable* ABS configurations. A configuration G of an ABS program is reachable if  $G_0 \Rightarrow^* G$ , for some *initial* configuration  $G_0$ . In an initial configuration of the ABS multicore program, all process queues are empty and the only active processes are those about to execute the run methods of the cores. This restriction allows us to use some general properties of the ABS semantics; e.g., upon return of a synchronous call, the local state of the calling object has not changed.

We can now express that an ABS program is a correct implementation of a TS model by proving that the following theorem holds:

DEFINITION 2 (CORRECTNESS). Given an ABS program and a TS model, let  $\alpha$  be an abstraction function from configurations of the ABS program to configurations of the TS model. The ABS program is a correct implementation of the TS model, if for any reachable configuration G and transition  $G \Rightarrow G'$  of the ABS program we have that  $\alpha(G) = \alpha(G')$  or  $\alpha(G) \rightarrow \alpha(G')$ .

Because of the general confluence property of the ABS semantics, it suffices to verify the annotations of methods in terms of the abstraction function  $\alpha$  to prove that  $\alpha$  is a simulation relation. The general idea is that for each transition  $G \Rightarrow G'$  that results from the execution from one stable point to a next one (or to termination), we have to show that  $\alpha(G')$  results from  $\alpha(G)$  by applying the enabled rule from the TS model associated with the initial stable point. In case no rule from the TS model is enabled, we have a "silent" step, that is,  $\alpha(G) = \alpha(G')$ .

## 4 A TS MODEL FOR MULTICORE MEMORY SYSTEMS

Design decisions for programs running on top of a multicore memory system can be explored using simulators (e.g., [15, 18, 44, 47]). Bijo et al. developed a TS model for multicore memory systems [13, 14]. Taking this TS model as a starting point, we will study how a parallel simulator can be developed in ABS which implements the TS model and use this development to discuss the details of our proof methodology for program correctness. We first introduce the main concepts of multicore memory systems and then look at their formalization in terms of a TS model.

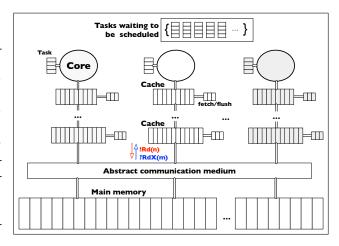

## 4.1 A Short Overview of Multicore Memory Systems

A multicore memory system consists of cores that contain *tasks* to be executed, the *data layout* in main memory (indicating where data is allocated), and a system *architecture* consisting of cores with private multi-level caches and shared memory (see Figure 5). Such a system is parametric in the number of cores, the number and size of caches, and the associativity and replacement policy. Data is organized in blocks that move between the caches and the main memory. For simplicity, we abstract from the data content of the memory blocks, assume that the size of cache lines and memory blocks in main memory coincide and that a local reference to a memory block is represented directly by the corresponding memory address, and transfer memory blocks from the caches of one core to the caches of another core via the main memory. As a consequence, the tasks executed in the cores are represented as data access patterns, abstracting from their computational content.

```

Syntactic

categories.

Definitions.

cid \in CoreId

cf \in Config

::=\langle \overline{CR}, \overline{Ca}, M \rangle

caid ∈ CacheId

CR \in Core

:= cid \bullet rst

n \in Address

::= caid \bullet M \bullet dst

Ca \in Cache

st \in Status

::= \{mo, sh, inv\}

dap \in AccessPtns := \varepsilon \mid dap; dap \mid read(n) \mid write(n)

rst \in RunLang ::= dap \mid rst; rst \mid readBl(n) \mid writeBl(n)

dst \in DataLang ::= \varepsilon \mid dst + dst \mid \mathbf{fetch}(n) \mid \mathbf{fetchBl}(n)

| fetchW(n, n') | flush(n)

```

Fig. 6. Syntax of runtime configurations, where over-bar denotes sets (e.g.,  $\overline{CR}$ ).

Task execution on a core requires memory blocks to be transferred from the main memory to the closest cache. Each cache has a pool of instructions to move memory blocks among caches and between caches and main memory. Memory blocks may exist in multiple copies in the memory system. Consistency between different copies of a memory block is ensured using the standard cache coherence protocol MSI (e.g., [57]), with which a cache line can be either modified, shared or invalid. A modified cache line has the most recent value of the memory block, therefore all other copies are

Fig. 5. Abstract model of a multicore memory system.

*invalid* (including the one in main memory). A *shared* cache line indicates that all copies of the block are consistent. The protocol's messages are broadcast to the cores. The details of the broadcast (e.g., on a mesh or a ring) can be abstracted into an *abstract communication medium*. Following standard nomenclature, *Rd* messages request *read* access and *RdX* messages *read exclusive* access to a memory block. The latter invalidates copies of the block in other caches, to provide write access.

We summarize the operational aspects of cache coherency with the MSI protocol. To access data from a memory block n, a core looks for n in its local caches. If n is not found in shared or modified state, a read request !Rd(n) is broadcast to the other cores and to main memory. The cache can fetch the block when it is available in main memory. Eviction is needed if the cache is full, removing some memory block to free space. Writing to block n requires n to be in shared or modified state in the local cache; if it is in shared state, an invalidation request !RdX(n) is broadcast to obtain exclusive access. If a cache with block n in modified state receives a read request ?Rd(n), it flushes the block to main memory; if a cache with block n in shared state receives an invalidation request ?RdX(n), it invalidates the cache line; the requests are discarded otherwise. Read and invalidation requests are broadcast instantaneously in the abstract model, reflecting that signalling on the communication medium is orders of magnitude faster than moving data to or from main memory.

# 4.2 A TS Model of Multicore Memory Systems

The multicore TS model describes the interactions between a core, caches, and the main memory in the multicore memory system. It further includes labeled transitions to model instantaneous broadcast. The multicore TS model is parametric in the number of cores and caches. The multicore TS model [13, 14] is shown to guarantee correctness properties for data consistency and cache coherence (see, e.g., [20, 58]), including the preservation of program order in each core, the absence of data races, and that stale data is never accessed.

In this paper, we present a simplified version of the multicore TS model which, in its original and more complex form, was introduced in [13, 14] and implemented as a correct distributed system in [9]. This simplified version allows us to focus on the main challenges of a correct distributed implementation. The runtime syntax is given in Figure 6. A configuration cf is a tuple consisting of a main memory M, cores  $\overline{CR}$ , caches  $\overline{Ca}$  (we abstract from the task queue, which contains all tasks waiting to be scheduled). A core  $(cid \bullet rst)$  with identifier cid executes runtime statements rst. A cache  $(caid \bullet M \bullet dst)$  with identifier caid has a local cache memory M and data instructions dst. We assume that the cache identifier caid encodes the cid of the core to which the cache belongs and its level in the cache hierarchy. We use  $Status_{\perp}$  to denote the extension of the set  $\{mo, sh, inv\}$  of status tags with the undefined value  $\perp$ . Thus, a memory  $M: Address \rightarrow Status_{\perp}$  maps addresses n to either a status tag st or to  $\perp$  if the memory block with address st is not found in t.

Data access patterns dap model tasks consisting of finite sequences of  $\mathbf{read}(n)$  and  $\mathbf{write}(n)$  operations to address n (that is, we abstract from control flow operations for sequential composition, non-deterministic choice, repetition, and task creation). The empty access pattern is denoted  $\varepsilon$ . Cores execute runtime statements rst, which extend dap with  $\mathbf{readBI}(n)$  and  $\mathbf{writeBI}(n)$  to block execution while waiting for data. Caches execute data instructions from a multiset dst to fetch or flush a memory block with address n; here,  $\mathbf{fetch}(n)$  fetches a block with address n,  $\mathbf{fetchBI}(n)$  blocks execution while waiting for data,  $\mathbf{fetchW}(n,n')$  waits for a memory block n' to be flushed before fetching n (this is needed when the cache is full), and  $\mathbf{flush}(n)$  flushes a memory block.

The connection between the main memory and the caches of the different cores is modelled by an *abstract communication medium* which allows messages from one cache to be transmitted to the other caches and to main memory in a parallel instantaneous broadcast. Communication in the abstract communication medium is captured in the TS model by label matching on transitions. For any address n, an output of the form !Rd(n) or !RdX(n) is broadcast and matched by its dual of the form ?Rd(n) or ?RdX(n). The syntax of the model is further detailed in [13, 14].

In the next section, we will introduce the rules that describe the interaction between core and cache incrementally when discussing their ABS implementation. (For a complete overview of the transition rules, we refer to Appendix C.) The following auxiliary functions are used in the transition rules:

- *next*(*caid*) for a cache identifier *caid* (respectively, *next*(*cid*) for a core identifier *cid*) gives the next-level cache, if it exists, and otherwise returns ⊥, representing 'undefined';

- status(M, n) returns the status of block n in memory M or  $\bot$  if the block is not found in M; and

- *select*(*M*, *n*) determines the address where a block *n* should be placed in the cache memory *M*, based on a cache associativity (e.g., random, set associativity or direct map) and a replacement policy (e.g., random or LRU—Least Recently Used).

The function *next* is assumed to be injective.

## 5 THE ABS MODEL OF THE MULTICORE MEMORY SYSTEM

This section describes the implementation of the multicore TS model by a model in ABS. We explain the structural and behavioural correspondence between these two models.

# 5.1 The Structural Correspondence

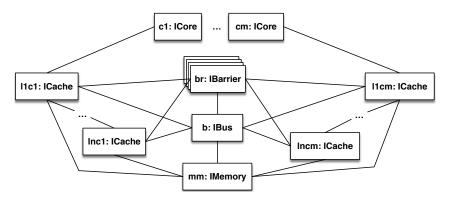

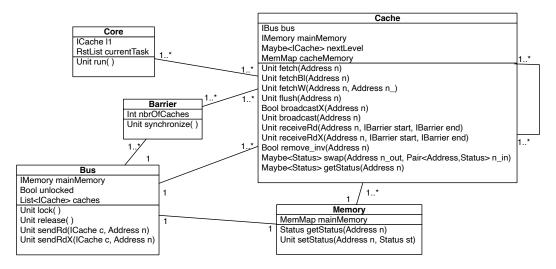

The runtime syntax of the multicore TS model is represented in ABS by classes, user-defined datatypes and type synonyms, outlined in Figures 8–9. An ABS configuration consists of class instances to reflect the cores with their corresponding cache hierarchies and the main memory. Object identifiers guarantee unique names and object references are used to capture how cores and caches are related. These references are encoded in a one-to-one correspondence with the naming scheme of the multicore TS model (and reflecting the implementation of the function *next*).

A core  $(cid \bullet rst)$  in the multicore TS model corresponds to an instance of the class Core in ABS, where a field currentTask of type RstList (as defined in Figure 9) represents the current list of runtime statements. Each instance of the class Core further holds a reference to the first-level cache. An important design decision we made is to represent the runtime statements rst (of a core in the multicore TS model) as an ADT (see Figure 9). A core in ABS then drives the simulation by processing these runtime statements which in general require information about the first-level cache. Alternatively, a core in ABS could delegate the processing of each runtime statement by calling corresponding methods of the first-level cache. However, this latter approach complicates the required callbacks.

A cache  $(caid \bullet M \bullet dst)$  in the multicore TS model corresponds to an instance of class Cache with a class parameter nextLevel which holds a reference to the next-level cache and a field cacheMemory which models the cache's memory M (of type MemMap, Figure 9). The multiset dst of a cache's data instructions (see Figure 6) is represented by corresponding *processes* in the message pool of the cache object in ABS. If the value of nextLevel is Nothing, then the object represents the last-level cache (in the multicore TS model, the function next returns  $\bot$  in the case of the last-level cache.

In addition, the ABS implementation of the global synchronization with labels !Rd(n) and !RdX(n) used in the multicore TS model is based on the global synchronization pattern as described in Figure 4. However, instead of distinguishing between these two labels by means of an additional parameter, we introduce two corresponding broadcast interfaces:

```

interface | Broadcast {

Bool broadcast(...);

Unit receiveRd (| Barrier start, | Barrier end, ...)}

interface | BroadcastX {

Bool broadcastX(...);

Unit receiveRdX (| Barrier start, | Barrier end, ...)}

```

The class Cache then provides an implementation of both interfaces following the template of the class Broadcast in Figure 4. The ABS class Bus, on the other hand, follows the template of the Synchronizer class with the two versions sendRd and sendRdX of the method sendSync.

The object diagram in Figure 7 shows an initial configuration corresponding to the multicore memory system depicted in Figure 5.

$<sup>^9\</sup>mathrm{The}$  ABS model for the multicore memory system can be found at https://abs-models.org/documentation/examples/multicore memory/

Fig. 7. Object diagram of an initial configuration.

Fig. 8. Class diagram of the ABS model.

```

data Rst = Read(Address) | ReadBl(Address) | Write(Address) | WriteBl(Address);

data Status = Sh | Mo | In;

type RstList = List<Rst>;

type Address = Int;

type MemMap = Map<Address,Status>;

```

Fig. 9. Abstract data types of the model of the multicore memory system.

## 5.2 The Behavioural Correspondence

We next discuss the ABS implementation of the transition rules of the multicore TS model, and the ABS synchronization patterns described in Section 2. We observe that the combination of asynchronous method calls and cooperative scheduling in ABS is crucial because of the interleaving inherent to the multicore TS model, which requires that objects are able to process other requests

while executing a method in a controlled way; e.g., caches need to flush memory blocks while waiting for a fetch to succeed.

5.2.1 The Annotated ABS Multicore Implementation. The classes Core and Cache pose the main implementation challenges. Here we explain the implementation of the run method (Figure 10) of the class Core (which is its only method) informally, in terms of its annotations (see Section 3.1). In Section 5.2.2, we introduce a formal semantics of these annotations as a high-level description of a simulation relation, which we use to prove the correctness of the ABS implementation.

The run method in the class Core may generate synchronous calls to the auxiliary methods in the class Cache, given in Figure 11. The method remove\_inv instantiates the test-and-set pattern of Figure 2. The method broadcastX is an instance of the global synchronization pattern described in Section 2, Figure 4. The method sendRdX, of the global synchronizer bus, asynchronously calls the method receiveRdX (see Figure 12) of all caches (except for the calling cache), using the barrier synchronization described in Section 2.

Since the stable point at the beginning of the run method has no associated annotation, by definition (see Section 3.1), for *any* path from the beginning of the method to a next stable point (or to termination) there is *no* corresponding transition rule (of the multicore TS model). For example, there is no transition rule corresponding to the case that the run method terminates when currentTask==Nil (note that because of the structural correspondence, the corresponding core has no runtime statements *rst* to execute). Similarly, there are no transition rules corresponding to the execution of the code from the beginning of the method to the synchronous calls to the auxiliary methods remove\_inv (Figure 10, Line 7) and getStatus (Figure 10, Lines 14, 18 and 31) of the first-level cache which, besides the pattern matching, only consists of the call itself.

The condition of the annotation removed==True: PRRD<sub>2</sub> (Figure 10, Line 7) associated with the synchronous call to the remove\_inv method describes the path which leads from its execution and returns via the **then**-branch of the subsequent **if**-statement to the termination of the run method (after it has called itself again asynchronously). According to the annotation, the execution of this path corresponds to the PRRD<sub>2</sub> transition rule:

```

(PRRD_{2})

next(cid) = caid \quad status(M, n) \in \{inv, \bot\}

(cid \bullet \mathbf{read}(n); rst), (caid \bullet \mathbf{M} \bullet dst) \rightarrow

(cid \bullet \mathbf{readBl}(n); rst), (caid \bullet \mathbf{M}[n \mapsto \bot] \bullet dst + \mathbf{fetch}(n))

```

This rule handles the case when a core intends to read a memory block with address n, which is not found in the first-level cache. The core will then be blocked (by adding a ReadBl(n) to the currentTask, using the list constructor Cons) while waiting for the memory block to be fetched, either from the lower-level caches or main memory. The condition as returned by the remove\_inv method signals that the status of the address of the first-level cache is undefined or invalid.

On the other hand, the condition removed==False describes the path which leads from its execution and return via the **else**-branch (Figure 10, Line 11), which also leads to the termination of this invocation of the run method. According to the annotation, the execution of this path corresponds to the PRRD<sub>1</sub> transition rule:

```

(PRRD_1)

next(cid) = caid \quad status(M, n) \in \{sh, mo\}

(cid \bullet \mathbf{read}(n); rst), (caid \bullet M \bullet dst) \to (cid \bullet \mathbf{rst}), (caid \bullet M \bullet dst)

```

```

Unit run() {

1

if (currentTask!=Nil) {

2

switch (currentTask) {

3

Cons(rst, rest) =>

4

switch (rst) {

5

Read(n) \Rightarrow \{

6

Bool removed = I1.remove_inv(n); // removed==True: PRRD2; removed==False: PRRD1

if (removed) {

8

11!fetch(n);

currentTask = Cons(ReadBl(n),rest); }

10

else {currentTask = rest; }

11

12

ReadBl(n) => {

13

Maybe<Status> status = 11.getStatus(n); // status!=Nothing: PRRD3

14

if (status != Nothing) { currentTask = Cons(Read(n),rest); }

15

16

Write(n) \Rightarrow {

17

Maybe<Status> status = 11.getStatus(n); // status==Just(Mo): PRWR1

18

switch (status) {

19

Just(Mo) => { currentTask = rest; }

20

Just(Sh) => {

21

Bool res = I1.broadcastX(n); // res==True: SynchX

22

if (res) { currentTask = rest; }

23

}

24

25

_ => {

Bool removed = I1.remove_inv(n); // removed == True: PRWR3

26

if (removed) { I1!fetch(n); currentTask = Cons(WriteBl(n),rest); }

27

}}

28

29

WriteBl(n) => {

30

Maybe<Status> status = I1.getStatus(n); // status!=Nothing: PRWR4

31

if (status != Nothing) { currentTask = Cons(Write(n),rest); }

32

}

33

}

34

35

this! run();

36

37

```

Fig. 10. Annotated run method of class Core.

This rule covers the case when the memory block to be read by a core is found in its first-level cache. Note that the condition as returned by the remove\_inv method implies that the status of the address of the first-level cache is either shared or modified.

Next, we consider the annotation status!=Nothing: PRRD<sub>3</sub> of the synchronous call to the getStatus method (Figure 10, Line 14).<sup>10</sup> Its condition describes the execution path which leads from the execution and return of the called getStatus method to termination of the run method via the **then**-branch of the subsequent **if**-statement (Line 15). According to the annotation, the

$<sup>^{10}</sup>$ Observe that the local variable status is of type Maybe, which means that the return value is Nothing or a value of type Status wrapped around the construct Just.

```

Maybe<Status> getStatus(Address n) { return lookup(cacheMemory,n); }

Bool remove_inv(Address n) {

1

Bool answer = False;

2

switch (lookup(cacheMemory,n)) {

3

Nothing => { answer = True; }

4

Just(In) =>{ cacheMemory = removeKey(cacheMemory,n); answer = True; }

5

_ => skip;

6

return answer;

8

9

Bool broadcastX(Address n) {

1

Bool res = False:

2

await bus!lock(); //(lookup(cacheMemory,n) == Just(Sh)): PRWR2

3

if (lookup(cacheMemory,n) ==Just(Sh)) {

4

mainMemory.setStatus(n,In);

5

bus.sendRdX(this, n);

6

cacheMemory = put(cacheMemory,n,Mo);

7

res = True;

8

bus.release();

10

return res;

11

12

```

Fig. 11. Methods getStatus, remove inv, and broadcastX of class Cache.

```

Unit receiveRdX(Address n, IBarrier start, IBarrier end) {

// lookup(cacheMemory,n))==Just(Sh): INVALIDATE-ONE-LINE;

2

// lookup(cacheMemory,n))!=Just(Sh): IGNORE-INVALIDATE-ONE-LINE

3

await start!synchronize();

4

switch (lookup(cacheMemory,n)) {

Just(Sh) => { cacheMemory = put(cacheMemory,n,In); }

6

_ => skip;

7

8

end.synchronize();

9

10

```

Fig. 12. Annotated receiveRdX method of class Cache.

execution of this path corresponds to the PRRD3 transition rule:

```

(PRRD_3)

next(cid) = caid \quad n \in dom(M)

(cid \bullet \mathbf{readBl}(n); rst), \ (caid \bullet M \bullet dst) \to (cid \bullet \mathbf{read}(n); rst), \ (caid \bullet M \bullet dst)

```

This rule unblocks the core from waiting when n (i.e., the block to be read) is found in the first-level cache. On the other hand, there does not exist a transition rule which corresponds to the execution path described by the condition status==Nothing. This path leads from the execution of the called

getStatus method directly to the termination of the run method without an update of the (local) state, e.g., currentTask is not updated. In other words, the evaluation of the statement readBl(n) in ABS involves *busy waiting* until the status returned by the first-level cache is defined. Alternatively, this could be implemented by calling a method of the first-level cache synchronously, which simply executes the statement **await** lookup(cacheMemory,n)!=Nothing.

The annotation of the synchronous call to method getStatus (Figure 10, Line 31) involves the transition rule

$$(PRWR_4)$$

$$next(cid) = caid \quad n \in dom(M)$$

$$(cid \bullet writeBl(n); rst), (caid \bullet M \bullet dst) \rightarrow (cid \bullet write(n); rst), (caid \bullet M \bullet dst)$$

This annotation is explained in a similar manner as the annotation of the synchronous call to the getStatus method on Line 14. This rule unblocks the core from waiting when n (i.e., the block to be written) is found in the first-level cache.

We now consider the annotation status==Just(Mo):  $PRWR_1$  of the synchronous call to the method getStatus (Figure 10, Line 18). Its condition describes the execution path which leads from the execution of the called getStatus method and subsequent execution of the **switch**-statement to termination of the run method. According to the annotation, the execution of this path corresponds to the  $PRWR_1$  transition rule:

$$(P_{R}W_{R_{1}})$$

$$next(cid) = caid \quad status(M, n) = mo$$

$$(cid \bullet write(n); rst), (caid \bullet M \bullet dst) \rightarrow (cid \bullet rst), (caid \bullet M \bullet dst)$$

This rule allows a core to write to memory block n if the block is found in a modified state in the first-level cache. On the other hand, in case the condition does not hold, according to the annotation no transition rules correspond to the execution paths which lead from the execution of the called getStatus method to the next stable points, i.e., the synchronous calls to the methods broadcastX and remove\_inv (Lines 22 and 26, respectively).

The condition of the annotation res==True: SynchX of the synchronous call to the broadcastX method (Figure 10, Line 22) of the first-level cache describes the path which leads from the execution of the broadcastX method, followed by the execution of the subsequent **if**-statement to termination of the run method (after an update of currentTask and calling the run method again asynchronously). According to the annotation, this path corresponds to the global synchronization rule

$$(SYNCHX)$$

$$CR \notin \overline{CR_1} \quad CR, \overline{Ca}, M \xrightarrow{!RdX(n)} CR', \overline{Ca'}, M'$$

$$\langle \overline{CR_1} \cup \{CR\}, \overline{Ca}, M \rangle \rightarrow \langle \overline{CR_1} \cup \{CR'\}, \overline{Ca'}, M' \rangle$$

where the second premise is generated by successive applications of the rule

$$Ca_{1} \notin \overline{Ca} \quad CR, \overline{Ca}, M \xrightarrow{!RdX(n)} CR', \overline{Ca'}, M' \quad Ca_{1} \xrightarrow{?RdX(n)} Ca_{2}$$

$$CR, \overline{Ca} \cup \{Ca_{1}\}, M \xrightarrow{!RdX(n)} CR', \overline{Ca'} \cup \{Ca_{2}\}, M'$$

This latter rule itself is triggered by the following rules

```

(PRWR_{2})

next(cid) = caid \quad status(M', n) = sh

(cid \bullet write(n); rst), (caid \bullet M' \bullet dst), M

\stackrel{!RdX(n)}{\longrightarrow} (cid \bullet rst), (caid \bullet M'[n \mapsto mo] \bullet dst), M[n \mapsto inv]

(Invalidate-One-Line)

status(M, n) = sh

(Ignore-Invalidate-One-Line)

status(M, n) \in \{inv, \bot\}

caid \bullet M \bullet dst \xrightarrow{?RdX(n)} caid \bullet M[n \mapsto inv] \bullet dst

caid \bullet M \bullet dst \xrightarrow{?RdX(n)} caid \bullet M \bullet dst

```

Together, these rules capture the broadcast mechanism for invalidation in the multicore memory system. Rule  $PRWR_2$  corresponds to the case where a core writes to a memory block n that is marked as shared in its first-level cache, which requires broadcasting an invalidation message, !RdX(n), to all the other caches. This is achieved by triggering the global synchronization rules SYNCHX and SYNCH-DISTX. While the former identifies the core CR that broadcasts the invalidation message, the latter recursively propagates the message, ?RdX(n), to the other caches. Depending on the local status of memory block n in the recipient cache, the recipient cache will either invalidate the local copy of the block (Invalidate-One-Line), or ignore the message (Ignore-Invalidate-One-Line).

To explain this application of the SYNCHX rule, we have a closer look at the definition of the broadcastX method. Its body involves an instance of the global synchronization pattern (Figure 4). As discussed in Section 2, because of the global confluence property, we may assume that its execution is *atomic*; i.e., its execution is not interleaved with any process that it has not generated. The synchronous call to the sendRdX method of the bus generates asynchronous calls to the receiveRdX method (Figure 12) of all caches except the one that initiated the global bus synchronization. Following the general global synchronization pattern (Figure 4), these method calls are synchronized by a start and an end barrier. The two conditions of the annotation at the beginning of the receiveRdX method describe the two possible execution paths and their corresponding transition rules Invalidate-One-Line and Ignore-Invalidate-One-Line.

If the condition res==True does not hold, according to the annotation no transition rule corresponds to the execution of broadcastX. In this case the bus synchronization, as invoked by the broadcastX method (Figure 11), failed because the status of the address of the first-level cache is not shared anymore (as required by the  $PRWR_2$  rule). Consequently, the processing of the statement write(n) fails and it will be processed again by the asynchronous self-call to the run method.

We conclude the informal explanation of the annotated run method with the annotation  $removed==True: PRWR_3$  of the synchronous call to the method  $remove\_inv$  (Figure 10, Line 26). Its condition describes the path that corresponds to the transition rule:

```

(PRWR_3)

next(cid) = caid \quad status(M, n) \in \{inv, \bot\}

(cid \bullet \mathbf{write}(n); rst), \ (caid \bullet M \bullet dst) \rightarrow

(cid \bullet \mathbf{writeBl}(n); rst), \ (caid \bullet M[n \mapsto \bot] \bullet dst + \mathbf{fetch}(n))

```

This rule handles the case when a core tries to write to a memory block with address n, which is either invalid or not found in the first-level cache. The core will then be blocked while the memory block is fetched from the lower-level caches or from the main memory. On the other hand, according to the annotation, no transition rule corresponds to the execution path that is described by the

negation of the condition (removed==False). As above, the run method terminates without having successfully processed the write(n) task, which will be evaluated again by the next asynchronous invocation of the run method. Note that this covers the case when the status returned by getStatus (Line 18) has changed; i.e., the status of the memory block is no longer undefined or invalid.

5.2.2 Correctness of the Annotated Multicore Implementation. We now consider the formalization of the correctness argument for the ABS implementation of the multicore system. First, we detail the construction of the abstraction function  $\alpha$ , which maps an ABS runtime configuration to the corresponding configuration of the TS model (see Figure 6). Recall that objects in the ABS semantics take the form  $\langle oid, \sigma, p, Q \rangle$ , where oid is the object identifier,  $\sigma$  assigns values to the object's field, p refers to the active process (either a closure  $(\tau, s)$  or the idle process), and Q the process queue (see Section 2.2). With no loss of generality, we use  $cid \in CoreId$  and  $caid \in CacheId$  to symbolically reference cores and caches in ABS runtime configurations, and identify the ABS data structures defined in Figure 9 with the corresponding TS data structures and their syntax as defined in Figure 6. To reduce notational overhead, we represent the ABS constructs, including the names of fields and local variables in italics to match the syntax of the TS model, e.g., WriteBl(n) is parsed to writeBl(n), Sh to sh, etc.

We explain the representation of the classes Core, Cache and Memory in the runtime configurations of the ABS semantics. The fields declared in these classes are summarised in Figure 13. An instance of the class Core is then represented by a runtime object  $\langle cid, \sigma, p, Q \rangle$ , where cid is the identifier of the core, and  $\sigma$  assigns to the field l1 the object identifier caid for the core's first-level cache and currentTask to the task's runtime statements rst, p is the active process and Q the process queue. Note that for

| Class  | Fields                 |

|--------|------------------------|

| Core   | l1, currentTask        |

| Cache  | nextLevel, mainMemory, |

|        | bus, cacheMemory       |

| Memory | mainMemory             |

Fig. 13. Domain of the field-assignment  $\sigma$  for the main ABS classes.

this class, the active process p will either be an activation of run or the idle process, and the process queue Q will only consist of the next call to run just before the current call to run terminates (since the interface of the class does not provide methods). An instance of class Cache is represented by a runtime object  $\langle caid, \sigma, p, Q \rangle$ , where caid is the object identifier and  $\sigma$  binds bus to the reference for the (single) instance of class Bus, mainMemory to the reference for the (single) instance of class Memory which represents the main memory, nextLevel to an identifier caid' for another instance of class Cache, and cacheMemory to a data structure M of type MemMap. The unique instance of class Memory is represented by a runtime object  $\langle main, \sigma, p, Q \rangle$  where main is the object identifier and  $\sigma$  binds mainMemory to a data structure M of type MemMap.

The abstraction function  $\alpha$  is now defined for instances of Core, Cache and Memory as follows:

```

\begin{array}{ll} \alpha(\langle cid,\sigma,p,Q\rangle) &= cid \bullet \sigma(currentTask) & Core \\ \alpha(\langle caid,\sigma,p,Q\rangle) &= caid \bullet \sigma(cacheMemory) \bullet \alpha(Q) + \alpha(p) & Cache \\ \alpha(\langle main,\sigma,p,Q\rangle) &= \sigma(mainMemory) & Main memory \end{array}

```

Note that for objects of classes Main and Core,  $\alpha$  abstracts from the process of the objects, while for objects of class Cache the processes of the queue Q that are generated by (asynchronous) calls to the methods fetch, fetchB, fetchW, and flush, are abstracted into the corresponding dst instructions in the TS model, capturing the method name and actual parameter of the processes; e.g., a process, generated by an asynchronous call to fetch(n), denoted by fetch(n), is abstracted into the corresponding fetch(n) instruction. This way,  $\alpha$  abstracts from the actual process executing the call. Further,  $\alpha$  abstracts from all the other processes. Instances of the ABS classes Barrier and Bus do not have a direct representation in the TS model.

For an ABS runtime configuration, which consists of a set of objects, the abstraction function returns the union of the abstraction of each of the objects. Given a runtime configuration G of the ABS multicore program such that every Core instance is associated with a singly-linked list of Cache instances (note that such a linked list is represented in the TS model by the auxiliary function next), we denote by  $\alpha(G)$  the result of the above translation to its cores and caches, and its single main memory.

We now consider the execution of the ABS multicore program. Recall from Section 2.2 that the transition relation  $\Rightarrow$  is between stable configurations in ABS. The following theorem states that the ABS multicore program is a correct implementation of the multicore TS model:

Theorem 2. Let G be a reachable stable global configuration of the ABS multicore program. If  $G \Rightarrow G'$  then  $\alpha(G) = \alpha(G')$  or  $\alpha(G) \rightarrow \alpha(G')$ .

For the proof, we need to reason about *arbitrary* ABS runtime configurations of the multicore program, e.g., abstracting from the number of cores and caches, we reason in terms of the *symbolic execution* of the ABS multicore program. We show by *static analysis* of the ABS program that the TS model provides a high-level description of the symbolic execution of the ABS multicore model, under the abstraction function  $\alpha$ . This static analysis relies on the fact that only a finite number of paths are possible from one stable point to another in the ABS multicore model. In fact, there are no **while**-statements or synchronous self-calls between two stable points in the ABS multicore program. Further, the Boolean conditions associated with the rule annotations can be used to statically identify the corresponding paths.

The overall idea of the symbolic execution of ABS programs is based on the distinction between local program variables (and fields) and global logical variables, which do not appear in programs but are used to describe symbolically the values of the program variables. Logical expressions (to be distinguished from the programming expressions) are constructed from these logical variables, using the built-in and user-defined data structures. We give ABS runtime objects  $\langle oid, \sigma, p, Q \rangle$  a symbolic interpretation, where oid is a logical variable (representing the symbolic value of **this**),  $\sigma$  binds fields to logical expressions, p is a symbolic process and Q is a logical expression denoting the process queue. A process is described symbolically by the pair  $(\tau, S)$ , where  $\tau$  binds the local variables to logical expressions and S is a symbolic representation of a statement. The abstraction function  $\alpha$  is then extended to the symbolic representation of the instances of the classes Core, Cache and Memory. Note that  $\alpha(\langle oid, \sigma, p, Q \rangle)$ , where  $\langle oid, \sigma, p, Q \rangle$  denotes a symbolic representation of such an instance, is itself a symbolic representation of a concrete instance of a core, cache or memory object in the TS multicore model.

Let  $C,D,\ldots$  denote symbolic states that consist of symbolic instances of the classes Core, Cache and Memory. As above, we denote by  $\alpha(C)$  the result of the abstraction  $\alpha$  to its (symbolic) cores, caches, and its single (symbolic) main memory in the TS multicore model. A *symbolic configuration*  $C \mid \phi$  additionally specifies a *path condition* by a logical expression  $\phi$  (which, as explained above, does not contain program variables). For a symbolic execution path from one stable point of the ABS multicore program to a next one, we show that the associated rule of the TS multicore model can be obtained as  $\alpha(C) \to \alpha(D)$  (modulo renaming of the logical variables), where  $C \mid \mathbf{true} \Rightarrow D \mid \phi$  denotes a symbolic execution of this path, starting from the symbolic state C and resulting in symbolic state D. The path condition  $\phi$  generated by the symbolic execution corresponds to the enabling conditions of the corresponding rule in the TS model.

We briefly explain the symbolic execution of the relevant rules of the ABS semantics. Assignment to an instance variable (a field) is described symbolically by the transition

$$\langle oid, \sigma, (\tau, x := e; S), Q \rangle, C \mid \phi \rightarrow \langle oid, \sigma[x := \theta(e)], (\tau, S), Q \rangle, C \mid \phi$$

where  $\theta = \sigma \cup \tau$  (i.e.,  $\theta$  denotes the union of the substitutions  $\sigma$  and  $\tau$ ),  $\theta(e)$  denotes the result of replacing every program variable x in e by  $\theta(x)$  and  $\sigma[x := \theta(e)]$  denotes the corresponding update of  $\sigma$ . We omit the similar rule for an assignment to a local variable (which will instead update  $\tau$ ).

The symbolic execution of Boolean conditions extends the path condition to capture an assumption about validity of the condition. In ABS, Boolean conditions can occur in **if**-, **await**- and **switch**-statements. The symbolic execution of an **if**-statement which assumes that the Boolean condition holds, is captured by

$$\langle oid, \sigma, (\tau, \mathbf{if} \ b \ \{S_0\}\{S_1\}; S), Q \rangle, C \mid \phi \rightarrow \langle oid, \sigma, (\tau, S_0; S), Q \rangle, C \mid \phi \wedge \theta(b)$$

where  $\theta = \sigma \cup \tau$ . Assuming that the Boolean condition does not hold, the symbolic execution of the **else**-branch is similar. The symbolic execution of an **await**-statement is captured by

$$\langle oid, \sigma, (\tau, \mathbf{await}\ b; S), Q \rangle, C \mid \phi \rightarrow \langle oid, \sigma, (\tau, S), Q \rangle, C \mid \phi \wedge \theta(b)$$

where  $\theta = \sigma \cup \tau$ . The symbolic execution of a **switch**-statement is captured by

$$\langle oid, \sigma, (\tau, \mathbf{switch} \ e \{ \dots e_i \Rightarrow S_i \dots \}; S), Q \rangle, C \mid \phi \rightarrow \langle oid, \sigma, (\tau', S_i; S), Q \rangle, C \mid \phi \wedge \theta (e = e_i)$$

where  $\tau'$  extends  $\tau$  by binding the fresh (local) variables appearing in  $e_i$  to the corresponding subterms of e, and  $\theta = \sigma \cup \tau'$ .

The symbolic execution of method calls extends the path condition to capture the assumption about the identity of the callee. The symbolic execution of an *asynchronous call* to a method m with body  $S_0$  and formal parameters  $x_1, \ldots, x_n$ , is captured by

$$\langle oid, \sigma, (\tau, e_0!m(\bar{e}); S), Q \rangle$$

,  $\langle oid', \sigma', p, Q' \rangle$ ,  $C \mid \phi \rightarrow \langle oid, \sigma, (\tau, S), Q \rangle$ ,  $\langle oid', \sigma', p, Q'' \rangle$ ,  $C \mid \phi'$

where  $\theta = \sigma \cup \tau$  and  $\phi'$  denotes the updated path condition  $\phi \land \theta(e_0) = oid'$ . Here, Q'' is obtained from Q' by adding the symbolic process  $(\tau_0, S_0)$ , where  $S_0$  denotes the body of the method m and  $\tau_0$  binds every formal parameter  $x_i$  (for i = 1, ..., n) to the logical expression  $\theta(e_i)$  (where  $\bar{e} = e_1, ..., e_n$ ).

The symbolic execution of a *synchronous call* is obtained by method inlining. Let  $\rightarrow^*$  denote the transitive closure of  $\rightarrow$ ; as before, *idle* denotes the terminated process (see in Section 2.2). The symbolic execution of a method m with body  $S_0$  and formal parameters  $x_1, \ldots, x_n$  is captured by

$$\langle oid', \sigma', (\tau_0, S_0), Q' \rangle, C \mid \phi \rightarrow^* \langle oid', \sigma'', (\tau', \mathbf{return} \ e), Q'' \rangle, C' \mid \phi' \rangle$$

$\langle oid, \sigma, (\tau, x := e_0.m(\bar{e}); S), Q \rangle, \langle oid', \sigma', idle, Q' \rangle, C \mid \phi \rangle$

$\langle oid, \sigma[x := \theta'(e)], (\tau, S), Q \rangle, \langle oid', \sigma'', idle, Q'' \rangle, C' \mid \phi' \wedge \theta(e_0) = oid' \rangle$

assuming that x is a field (the case of a local variable is treated similarly). Here,  $\theta' = \sigma'' \cup \tau'$  and, for every formal parameter  $x_i$  (for i = 1, ..., n),  $\tau_0$  binds  $x_i$  to the logical expression  $\theta(e_i)$  (where  $\bar{e} = e_1, ..., e_n$ ). As before,  $\theta = \sigma \cup \tau$ .

The correspondence between the concrete and symbolic semantics of ABS can now be formally expressed, following [22]. Let  $C \mid \mathbf{true} \Rightarrow D \mid \phi$  denote the symbolic execution from one stable point to a next one, and let  $\gamma$  assign values to the logical variables. For any logical expression e we denote by  $\gamma(e)$  its value with respect to  $\gamma$ , defined inductively in the standard manner. For any symbolic representation  $\langle oid, \sigma, p, Q \rangle$  of an ABS object, we define  $\gamma(\langle oid, \sigma, p, Q \rangle) = \langle \gamma(oid), \sigma', p', Q' \rangle$ , where  $\sigma'(x) = \gamma(\sigma(x))$  and  $\{p'\} \cup Q'$  is obtained from  $\{p\} \cup Q$  by replacing  $(\tau, S) \in \{p\} \cup Q$  by  $(\tau', S)$ , where, as above,  $\tau'(x) = \gamma(\tau(x))$ . Further, for any symbolic state C we denote by  $\gamma(C)$  the point-wise extension of  $\gamma$ .

Theorem 3. Let G and G' be stable configurations of the ABS multicore program. For every transition  $G \Rightarrow G'$ , there exists an assignment  $\gamma$  and a symbolic transition  $C \mid \mathbf{true} \Rightarrow D \mid \phi$  such that  $\alpha(\gamma(C)) = \alpha(G)$ ,  $\alpha(\gamma(D)) = \alpha(G')$ , and  $\gamma(\phi) = \mathbf{true}$ .